# Agilent Technologies

EducatorsCorner.com Experiments

## **Shift Register**

**By:** Dr. A. D. Johnson EECS: 1100 Digital Logic Design The University of Toledo

### 1. Objectives

- Getting familiar with the design of sequential circuits on the register transfer level,

Lab Assignment #10

- gaining experience in using functions of shift registers for performing register transfer operations,

- gaining a close insight into the functioning and properties of the universal shift register,

- developing skills in the composition and testing of sequential logic circuits

- developing skills in generating timing signals.

# 2. Prelab Assignment

#### 2.1 UNIVERSAL SHIFT REGISTER USED AS AN I/O PORT REGISTER

- 2.1.1 The universal shift register 74LS194A is discussed in the TTL Data Book. Data sheets of the 74LS194A are also available in the TTL Data Book.

- 2.1.2 Using the information from the Data sheets of the 74LS194A, compile an Operation table of the 74LS194A. Show the compiled table as table T2.1-1.

- Hint#1 The Operation table is an excerpt from the function table of the 74LS194A which is given in the data sheets. It should show the four combinations of the logical values of the mode control signals S<sub>0</sub> and S<sub>1</sub> on the left side, and the description of the corresponding register operations on the right side.

| Operation code |                | Posister operation |

|----------------|----------------|--------------------|

| S <sub>0</sub> | S <sub>1</sub> | Register operation |

| 0              | 0              |                    |

| 0              | 1              |                    |

| 1              | 0              |                    |

| 1              | 1              |                    |

- **2.1.3** Design a sequential logic circuit in which two universal shift registers 74LS194A are interconnected to perform the following register transfer operations:

- a) registers R<sub>L</sub> and R<sub>M</sub> are parallely loaded with the BCD encoded nonzero LSDs of the birthdays of the two Lab team members;

- b) the contents of both registers are kept unchanged for four clock periods.

- c) the shift right operation is used to transfer the contents of register  $R_L$  to register  $R_M$ , while concurrently transferring the contents of the register  $R_M$  to  $R_L$ ;

- d) the shift left operation is used to transfer the contents of register R<sub>M</sub> back to register R<sub>L</sub>, while the contents of the register R<sub>M</sub> are replaced by logical 1's;

- 2.1.4 Prepare a computer generated drawing of the designed sequential logic circuit; show the drawing as Figure 2.1-1(a).

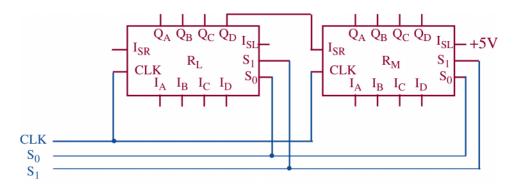

- **Hint#2** To help you start the circuit design, a partial connection of two 74LS194A universal shift registers is shown in Figure A.2-1.

- 2.1.5 Design a physical layout of the logic circuit shown in Figure 2.1-1(a). Prepare a computer generated drawing of the physical layout and show it as Figure 2.1-1(b). Provide the IC package pinouts on both drawings of Figure 2.1-1.

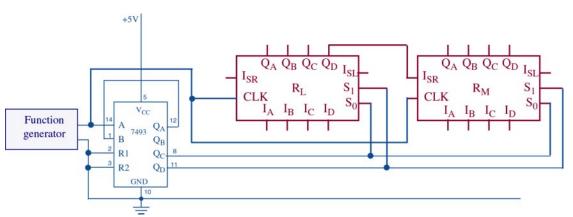

- **Hint#3** Consider generating the control signals using the IC 7493 connected as a binary counter, as shown in Figure A.4-1 and,

- connecting the clock input of the registers to the function generator signal,

- connecting the control signal S<sub>0</sub> of the registers to the Q<sub>c</sub> output of 7493,

- connecting the control signal  $S_{\rm 1}$  of the registers to the  $Q_{\rm D}$  output of 7493.

# 3. Lab Equipment and Circuit Components

#### **3.1 EQUIPMENT**

Equipment to be used includes:

- Proto boards: Global PB-104, or PB-105,

- Agilent E3631A DC power supply,

- Function generator: Agilent 33120A,

- Mixed-Signal oscilloscope Agilent 54645D,

- Dell GxaEM computer system.

#### **3.2 LOGIC GATE AND CIRCUIT COMPONENTS**

- integrated circuit 7493, 4-bit ripple counter (1)

- integrated circuit 74LS194, 4-bit universal shift register (2)

# 4. Lab Experiment

#### **4.1 REGISTER TRANSFERS**

4.1.1 Using as a reference the prepared physical circuit diagram of Figure 2.1-1(b), construct the circuit in which the two shift registers will perform the data transfers specified in Section 2.1.3. Figure A.4-1 shows a partial test circuit for experimenting with the shift register 74LS194A, in which the function generator and a binary counter serve as a generator of timing signals.

Figure A.4-1 A partially designed ciircuit for experimenting with the universal shift register.

- 4.1.2 Connect the digital channels D0 through D12 of the Mixed-Signal oscilloscope Agilent 54645D to the circuit constructed under 4.3.1:

- digital channel D0: to the clock signal input of the shift registers 74LS194A,

- digital channel D1: to the mode control input S<sub>0</sub> of the shift registers 74LS194A,

- digital channel D2: to the mode control input S<sub>1</sub> of the shift registers 74LS194A,

- digital channel D3: to the input  $I_{SR}$  of the register  $R_L$ ,

- digital channels D4:D7 to the outputs  $Q_{\text{A}}{:}Q_{\text{D}}$  of the register  $R_{\text{L}}$  .

- digital channel D8: to the input  $I_{\text{SL}}$  of the register  $R_{\text{M}},$

- digital channels D9:D12 to the outputs  $Q_A:Q_D$  of the register  $R_M$ . Establish a ground connection. Turn on digital channels D0 through D12, and rename the channels D0 through D12 as: CLK, S<sub>0</sub>, S<sub>1</sub>, I<sub>SRL</sub>, Q<sub>AL</sub>, Q<sub>BL</sub>, Q<sub>CL</sub>, Q<sub>DL</sub>, I<sub>SLM</sub>, Q<sub>AM</sub>, Q<sub>BM</sub>, Q<sub>CM</sub>, and Q<sub>DM</sub>, respectively.

- 4.1.3 Adjust the frequency of the Agilent 33120A function generator to 1MHz. Set the triggering mode of the Agilent 54645D to combination 11 on channels D1 and D2. Hit the key Single on the Agilent 54645D. Adjust the display so that the combination 11 of control signals variables  $S_0$  and  $S_1$  values is positioned at the left side of the screen, and that the whole screen shows ten percent more than two periods of the control signal  $S_1$ .

- 4.1.4 Turn off the digital channel D0, and save the Screen Image of the correct waveforms of channels D1 through D12 to a file named L10\_414.tif on the Dell GxaEM computer system. (Alternatively, use the Screen Capture tool.)

#### 4.2 TRANSFER OF CAPTURED WAVEFORMS.

Transfer (ftp) the files L10\_\*.tif from the Dell GxaEM computer system to your personal College of Engineering computer account.

### 5. Lab Report

To be considered complete, the lab report must contain the following,

- 1. Cover sheet Lab style, filled out,

- 2. The Operation table prepared under 2.1.

- 3. The logical and physical circuit diagrams prepared under 2.1.

- 4. The waveforms obtained in experiment 4.1.

- 5. Answers to all questions asked in conjunction with experiments 4.1.

- 6. A report on items not already included under 1. through 5. above, which includes:

- a discussion of the insights gained through the conducted experiments,

- textual description and graphical/ tabular illustration of the design procedure(s),

- description of implemented testing procedures,

- conclusions reached as a result of performing the lab experiment,

- comments and suggestions that might lead to easier and/or deeper understanding of the topics covered by the assignment.